Abstract

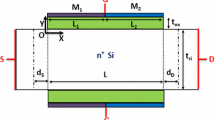

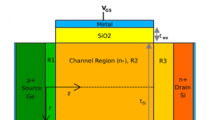

Analytical models for the electric potential, threshold voltage and drain current of long-channel junctionless (JL) double-gate (DG) field-effect transistors (FET) are presented. A regional method is used to solve the Poisson equation under different gate biases, and the electric potential is obtained. With the potential model, an analytical expression for the threshold voltage is achieved. An expression for the drain current is derived from the potential model. The analytical results are compared with simulations, and excellent agreements are observed. The models accurately describe the characteristics of JLDG FETs, and they are very helpful for the design and optimization of devices.

Similar content being viewed by others

References

G.-X. Hu, R. Liu, T.-A. Tang and L.-L. Wang, J. Korean Phys. Soc. 52, 1909 (2008).

C.-W. Lee, A. Afzalian, N. Dehdashti Akhavan, R. Yan, I. Ferain and J.-P. Colinge, Appl. Phys. Lett. 94, 053511 (2009).

J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy and R. Murphy, Nat. Nanotech. 5, 225 (2010).

J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, A. N. Nazarov and R. T. Doria, Appl. Phys. Lett. 96, 073510 (2010).

L. Ansari, B. Feldman, G. Fags, J.-P. Colinge and J. C. Career, Appl. Phys. Lett. 97, 062105 (2010).

C.-W. Lee, A. N. Nazarov, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, R. T. Doria and J.-P. Colinge, Appl. Phys. Lett. 96, 102106 (2010).

J. P. Duarte, S.-J. Choi, D.-I. Moon and Y.-K. Choi, IEEE Electron Device Lett. 32, 704 (2011).

A. M. Ionescu, Nat. Nanotech. 5, 178 (2010).

X. Jin, X. Liu, M. Wu, R. Chuai, J.-H. Lee and J.-H. Lee, Solid State Electron. 79, 206 (2013).

Z. Chen, Y. Xiao, M. Tang, Y. Xiong, J. Huang, J. Li, X. Gu and Y. Zhou, IEEE Trans. Electron Devices 59, 3292 (2012).

X. Jin, X. Liu, M. Wu, R. Chuai, J.-H. Lee and J.-H. Lee, J. Phys. D: Appl. Phys. 45, 375102 (2012).

T.-K. Chiang, IEEE Trans. Electron Devices 59, 2284 (2012).

J. P. Duarte, M.-S. Kim, S.-J. Choi and Y.-K. Choi, IEEE Trans. Electron Devices 59, 1008 (2012).

Z.-M. Lin, H.-C. Lin, K.-M. liu and T.-Y. Huang, Jpn. J. Appl. Phys. 51, 02BC14 (2012).

Taurus Medici, Medici User Guide, Version A-2008.09, Synopsys Inc (2008).

E. Gnani, A. Gnudi, S. Reggiani and G. Baccarani, IEEE Trans. Electron Devices 58, 2903 (2011).

C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi and J.-P. Colinge, Solid State Electron. 54, 97 (2010).

Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices (Cambridge University Press, Cambridge, 1998).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ding, Z., Hu, G., Liu, R. et al. Analytical models for the electric potential, threshold voltage and drain current of long-channel junctionless double-gate transistors. Journal of the Korean Physical Society 62, 1188–1193 (2013). https://doi.org/10.3938/jkps.62.1188

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.3938/jkps.62.1188